Timing error in sampling, and balanced ADC/clock choice

Timing error in sampling, and balanced ADC/clock choice

It is common for DSP systems to be designed a bit poorlly in terms of the balance between ADC accuracy and clock accuracy. I think this is becaue many designers do not realise that the two are linked: error in the clock timing leads to errors in the sampled signal.

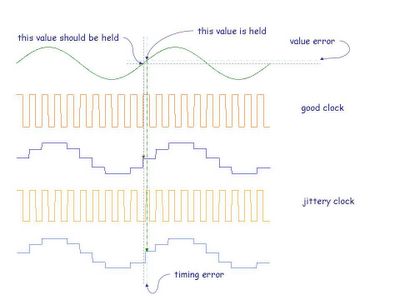

The diagram shows an analogue signal which is held on the rising edge of a clock signal. If the clock edge occurs at a different time than expected, the signal will be held at the wrong value. In the diagram, the signal is rising and so the held value is higher than it should be.

Errors introduced by timing jitter are as important as those caused by quantization, but are often forgotten. It is sadly common to see DSP systems where a lot of care has gone into the analog design and the selection of analog-to-digital converters with high precision and accuracy, but where the design is let down by a poor quality clock. A good design would balance the choice of clock accuracy against the ADC, and the fastest changing signals that are of interest. This becomes more important as we sample signals close to their Nyquist frequency.

Errors due to timing jitter depend on the rate of change of the signal (quantization errors depend on the instantaneous value of the signal). Sadly, these errors - like quantization errors - are both non linear and signal dependent, so are intractable to calculate.

Comments

Post a Comment